FPGA(3)--VHDL 及原理图 --4 位全加器

[](()一、实验目的

掌握例化语句的使用方法,掌握使用程序文本和原理图结合方法设计电路,掌握利用包含算术操作符的重载函数的使用。

[](()二、实验内容

首先用 VHDL 语言设计 1 位全加器,仿真验证其正确性,并将其封装成一个元件;设计串行 4 位加法器的电路,调用 1 位全加器设计 4 位加法器的原理图。通过编译、仿真验证功能正确性。

直接通过调用算术操作符的重载函数,利用 VHDL 语言设计 4 位全加器。通过编译、仿真验证功能正确性。

[](()三、实验设计

1.在上一个实验中已经用 VHDL 语言设计 1 位全加器,且仿真验证其正确性。如下即为 1 位全加器的 VHDL 描述。其原理在上一个实验已经说明,这里不再赘述。(可见上一篇)

Library Ieee; --全加器顶层设计描述

Use Ieee.Std_Logic_1164.All;

Entity f_adder is

Port (ain,bin,cin : in Std_Logic;

sum,cout : out Std_Logic);

End Entity f_adder;

Architecture Bhv of f_adder is

component h_adder --调用半加器声明

port (a,b : in Std_Logic; co,so : out Std_Logic);

End component h_adder;

signal so1,co1,co2 : Std_Logic; --定义三个信号变量作为内部的连接线

begin

u1: h_adder Port Map (a=>ain,b=>bin,so=>so1,co=>co1); --例化语句

u2: h_adder Port Map (a=>so1,b=>cin,so=>sum,co=>co2);

cout <= co1 or co2;

End Architecture Bhv;

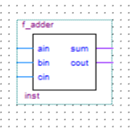

2.将其封装成一个元件。

①file→New,选 block diagram/schematic 创建原理图文件,保存一下。

②回到1位全加器 VHDL 描述页面,选 file→create/update→create symbol files for current file,把编写的代码封装成一个元 《一线大厂 Java 面试题解析+后端开发学习笔记+最新架构讲解视频+实战项目源码讲义》无偿开源 威信搜索公众号【编程进阶路】 件。

③回到创建的原理图文件,按工具条上的 symbol tool,再按 project,就可以看见该封装元件了。

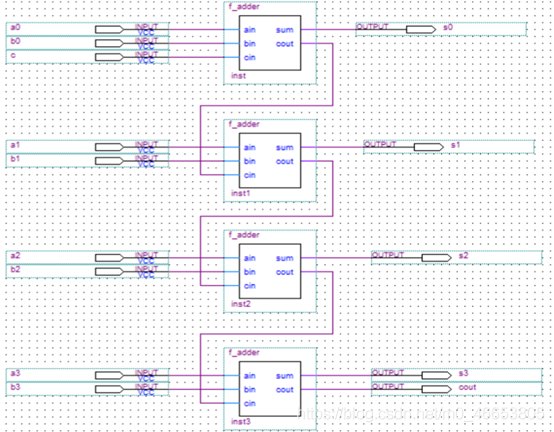

3.调用1位全加器元件设计 4 位加法器的原理图。如图即为设计的电路图。

ain、bin 和 cin 为输入信号,其中 cin 为前一位给的进位信号。sum 为求和结果输出,而 cout 为进位输出。1、2、3则为由低到高的四位。

4. 直接通过调用算术操作符的重载函数,利用 VHDL 语言设计 4 位全加器。代码如下图。data 的最高位则作为进位信号。

评论