国产 EDA 验证调试工具实现破局 助力芯片设计效率提升

经过数十年的发展,如今芯片设计的每个环节已离不开 EDA 工具的参与,涉及验证、调试、逻辑综合、布局布线等全流程。尤其是在关键的验证和调试环节,可谓是打通芯片流片的“任督二脉”,如果在这一环节受阻,那带来的“次生伤害”将难以想象。

特别是在当前国内 EDA 工具市场份额大多被国外巨头占有的情形下,一方面美国不断加大制约力度,“卡脖子”强度愈演愈烈;另一方面国际巨头工具大多越来越趋向于封闭流程。伴随着国内半导体业的蓬勃发展,国内 EDA 厂商如何着力解决工具从 0 到 1 的问题已成为时代的新使命。

看准这一契机,在 EDA 工具领域多点布局的上海合见工业软件集团有限公司(以下简称“合见工软”)近日推出了全新的 UVD 调试工具,以助力国内半导体设计厂商在验证和调试环节“通关”。

验证和调试需协同作战

之所以验证和调试至关重要,与数字芯片的设计需求和设计公司的产品迭代息息相关。

目前数字芯片的规模动辄上百亿门,且随着工艺的进阶,流片成本居高不下,流片失败的损失难以估量。更重要的是,重新设计不仅意味着巨量的研发成本投入,更会导致错失产品上市的时间窗口,错过发展壮大的时机。这对任何一家设计公司来说,都是难以承受之重。

芯片从设计到生产之前的流程中的诸多环节都离不开验证和调试,验证是为了确保设计符合功能和性能的要求,调试则是针对验证过程中发现的缺陷,尽早尽快地找出引起问题的真正原因以便修复,也因而,验证和调试成为解锁流片成败的关键环节。

“随着 SoC 芯片复杂度、集成度的提升和规模的扩大,验证工作的占比越来越高,可达到 70%以上,一般在设计团队中的基本配置是一个设计工程师要配备 2-3 个验证工程师。其中,调试的工作量则可占到验证工作的 40%以上。”合见工软资深研发总监高波以数字道出了验证和调试的“责任”重大。

相应地,这对验证和调试工具的挑战也与日俱增。

高波指出,验证工具和调试工具相辅相成,使命是快速实现验证收敛。保证覆盖率、充分并且尽早尽快地发现问题是对验证工具的挑战;调试工具则需要帮助用户更快地分析并解决功能、性能的问题,同时针对覆盖率相关问题的分析和调试可以加快覆盖率收敛。

此外,协同“作战”也是必要条件。高波进一步提到,在验证层面,涉及形式验证、FPGA 原型验证等不同的验证工具,为满足验证需求,不仅要求验证工具可协同工作,互相配合来达到充分的验证覆盖率,实现验证收敛;同时,调试工具作为一个平台应可支持所有验证工具的调试,并能支持不同验证工具协同仿真情况下的调试。

实现从 0 到 1 突破

不得不说,国际厂商在 EDA 验证和调试工具领域已然占据了先发地位,但对于国内蔚然兴起的 EDA 厂商来说,仍有角力的空间和破局的机会。

“验证和调试工具的架构和技术都需随着验证流程和方法学的发展而不断创新,国外厂商因长期的积累转身难免有包袱。在当下的时间节点,国内 EDA 厂商可以站在更高的起点,以全面的验证全景图为基础来设计产品的架构和功能,解决从 0 到 1 的问题,实现新的突破。” 高波对此充满信心。

显然,着眼于调试工具需求深耕细作、打造稳定高效的验证调试平台成为国内 EDA 厂商的重要任务。

高波提到,业界对调试工具的要求侧重于:从性能来说,要保证高性能、大容量;从易用性入手,需简洁易用、使用流畅,以全面保证调试的高效率。此外,在系统层面,需全面支持各种不同验证工具之间的协同仿真。

在这一过程中,更要注意与时俱进。高波表示,验证和调试工具在迭代过程中,要不断引入验证方法学和流程的创新,不仅支持功能的调试,还应拓展至功耗、覆盖率、安全等方面的调试;不仅要支持不同设计层级如 RTL 和 Gate 级的需求,还要支持事务级和系统级的验证调试。

“只有不断内外兼修,才能不断提高验证调试效率,加速验证收敛。”高波明确说。

对于国内验证和调试 EDA 厂商的发展路径,高波认为,既要稳扎稳打,也要布局长远。

“在打造出满足上述需求的调试平台之后,要扎实落地于国内半导体客户实际项目的应用,解决项目中调试的问题。并且,要以开放的心态拥抱本土客户的实际需求,实现差异化优势。在产品实现可用之后,可进一步加强通力合作,持续打磨产品,不断突破现有工具的技术包袱和技术壁垒,进一步提升验证和调试效率,实现好用耐用,走向双赢。”高波提出了中肯的建议。

UVD 的新进阶

基于在验证和调试工具的深刻洞察,加之合见工软团队在数字芯片验证领域累积的技术资源,以及不破不立的架构创新,合见工软先声夺人,在着力研发多种核心的验证工具时就已经开始在调试工具方面持续投入,而今迎来了 UVD 的上市。

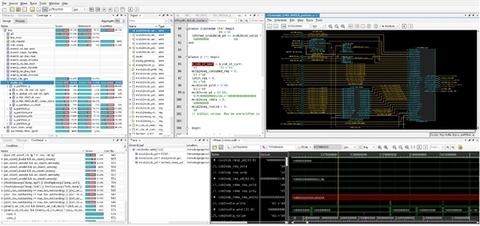

(图:UVD 主界面)

高波详细介绍道,合见工软 UVD 的优势体现在一是简洁易用,采用了先进的 UI 技术,界面简洁,根据所用的功能自适应,大幅提升用户体验。二是高效率、高性能,体现在大规模数据的处理效率和交互式性能上,如高性能的波形可与当前市场上的主流产品竞争,跟 VCD(Value Change Dump)的压缩比可达几十到上千倍。

更值得一提的是,合见工软 UVD 在架构和数据接口的设计上“为长远计”:支持不同验证工具的调试和不同工具间的数据统一共通、协同调试。

而这与合见工软蓄势发布的多款 EDA 产品和解决方案,包括数字仿真器、FPGA 原型验证系统、先进封装协同设计环境等,在高难度的数字验证、协同设计等领域率先突围奠定的基石可谓是相辅相成、交相辉映。

具体来看,合见工软 UVD 提供统一的波形和覆盖率数据接口,可与其他验证工具集成,促进不同验证工具间的数据整合和协同。这是目前很多主流工具还不支持的。另外,UVD 基于原生架构可以支持测试环境、设计以及覆盖率等的集成调试,例如 UVD 的源代码窗口已经预留了 IDE 的支持,将来很容易扩展支持 IDE,帮助设计工程师提高效率。

除此以外,合见工软所有产品都基于创新设计,充分考虑了不同产品之间的协同。比如:UVD 可以与合见工软的验证测试管理平台 VPS 互相配合,加速回归测试中缺陷和覆盖率的调试。

“合见工软已然构建了相对完整的 EDA 数字验证解决方案,作为调试工具,UVD 在客户的试用中已得到了积极的反馈。”或许客户的认同是证明 UVD 实力的最佳佐证。

如今国内半导体设计厂商技术飞速发展,也诞生了越来越多世界级的 IC 设计公司,在这一乐观态势下,合见工软深刻意识到,国内 EDA 厂商通过与 IC 厂商互促互进,将进一步夯实本土厂商放眼全球的基础。

在持续取得“开门红”之后,顺势而为的合见工软也有了更高远的目标。

高波最后表示,合见工软在验证领域拥有众多资深专家,技术团队非常有经验。合见工软将持续结合本土特有的优势,保持开放的心态,拥抱开放的架构,推动建立良好的 EDA 生态圈,同时在国内验证和调试 EDA 工具领域创新架构、持续打磨,助力国内半导体设计公司全流程服务。

评论