Verilog HDL 门级建模

⭐本专栏针对 FPGA 进行入门学习,从数电中常见的逻辑代数讲起,结合 Verilog HDL 语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机 FSM 进行剖析与建模。🔥文章和代码已归档至【Github 仓库:hardware-tutorial】,需要的朋友们自取。或者关注公众号【AIShareLab】,回复 FPGA 也可获取。

基本概念

结构级建模: 就是根据逻辑电路的结构(逻辑图),实例引用 Verilog HDL 中内置的基本门级元件或者用户定义的元件或其他模块,来描述结构图中的元件以及元件之间的连接关系。

门级建模: Verilog HDL 中内置了 12 个基本门级元件(Primitive,有的翻译为“原语”)模型,引用这些基本门级元件对逻辑图进行描述,也称为门级建模。

基本门级元件(Primitive : 原语)

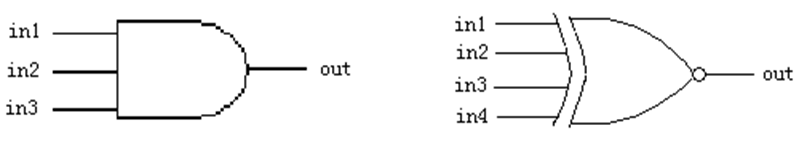

多输入门:and、nand、or、nor、xor、xnor

只有单个输出, 1 个或多个输入

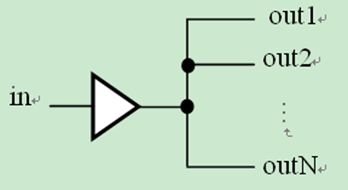

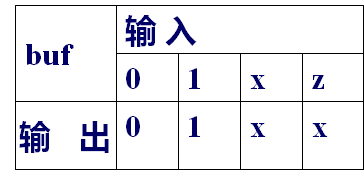

多输出门:not、buf

允许有多个输出, 但只有一个输入

三态门:bufif0、bufif1、notif0、notif1

有一个输出, 一个数据输入和一个控制输入

上拉电阻 pullup、下拉电阻 pulldown

多输入门

多输入门的一般引用格式为:

Gate_ name 共 6 个: and、nand、or、nor、xor、xnor

特点:

只有 1 个输出,

有多个输入。

基本门的调用方法举例:

对基本门级元件,调用名 A1、NX1 可以省略。

若同一个基本门在当前模块中被调用多次,可在一条调用语句中加以说明,中间以逗号相隔。

and、nand 真值表

多输出门

允许有多个输出,但只有一个输入。

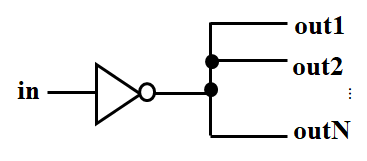

buf 真值表

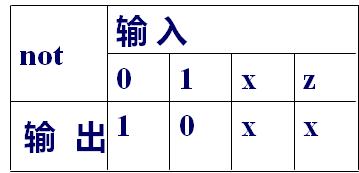

not 真值表

三态门

有一个输出、一个数据输入和一个输入控制。如果输入控制信号无效,则三态门的输出为高阻态 z。

门级建模举例

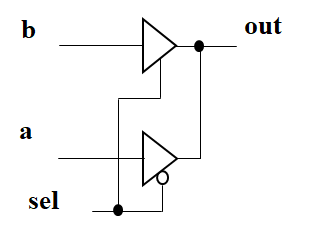

2 选 1 数据选择器

小结:门级建模就是列出电路图结构中的元件,并按网表连接 。

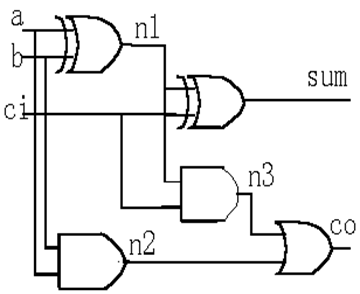

1 位全加器

若同一个基本门在当前模块中被调用多次,可在一条调用语句中加以说明,中间以逗号相隔。

门级描述小结

给电路图中的每个输入输出引脚赋以端口名。

给电路图中每条内部连线 取上各自的连线名。

给电路图中的每个逻辑元件取一个编号 (即“调用名”)。

给所要描述的这个电路模块确定一个模块名。

用 module 定义相应模块名的结构描述,并将逻辑图中所有的输入输出端口名列入端口名表项中,再完成对各端口的输入输出类型说明。

依照电路图中的连接关系,确定各单元之间端口信号的连接,完成对电路图内部的结构描述。

最后用 endmodule 结束模块描述全过程。

参考文献:

Verilog HDL 与 FPGA 数字系统设计,罗杰,机械工业出版社,2015 年 04 月

Verilog HDL 与 CPLD/FPGA 项目开发教程(第 2 版), 聂章龙, 机械工业出版社, 2015 年 12 月

Verilog HDL 数字设计与综合(第 2 版), Samir Palnitkar 著,夏宇闻等译, 电子工业出版社, 2015 年 08 月

Verilog HDL 入门(第 3 版), J. BHASKER 著 夏宇闻甘伟 译, 北京航空航天大学出版社, 2019 年 03 月

欢迎关注公众号【AIShareLab】,一起交流更多相关知识,前沿算法,Paper 解读,项目源码,面经总结。

版权声明: 本文为 InfoQ 作者【timerring】的原创文章。

原文链接:【http://xie.infoq.cn/article/2b5423be186d2188252603013】。未经作者许可,禁止转载。

评论