如何存储 1 个二进制位 & 锁存器的核心和本质

0 前言

本文将会以 R-S 锁存器为例,引出锁存器的核心和本质,之后再带你构建更多类型的锁存器,你能够:

感受到由浅入深的学习方式

体会到掌握核心本质的快感

深刻理解核心套外壳的设计理念

同时,强烈建议你使用 logisim 软件,边看文章边实践,这样能够加深理解,这款软件半小时即可入门,图形化的操作方式,简单又好用。

1 确立一个目标,提升你的认知效率

点进这篇文章,我想你是非常想要学会锁存器相关知识的,那么,为了进一步提高你的认知效率,我先给你定下一个目标,带着这个目标,再去一步一步寻找和学习相关知识,并且,你应该使用软件,在实践中学习,这么一来,你的认知效率将会翻倍。

我们都知道计算机的硬盘和内存,我们也知道,这些设备能够存储数据,并且这些数据是二进制信息,也就是 0、1 的各种排列组合,那么,你是否曾经产生疑惑,4GB、16GB,乃至 1TB 的信息,是如何被存储的?

今天让我们来解答这个问题,我们先不管 1TB 的信息如何存储的,今天我们就谈:如何存储 1 位二进制信息,也就是如何存储一个 0 或者一个 1。

我们需要制作一个器件,能够存储一个 0 或者一个 1。这个器件,就是 R-S 锁存器,在通电状态下,它能够**锁住(存储)1 个二进制位,也就是1 bit**。

让我们来一步步地揭开它的神秘面纱吧!

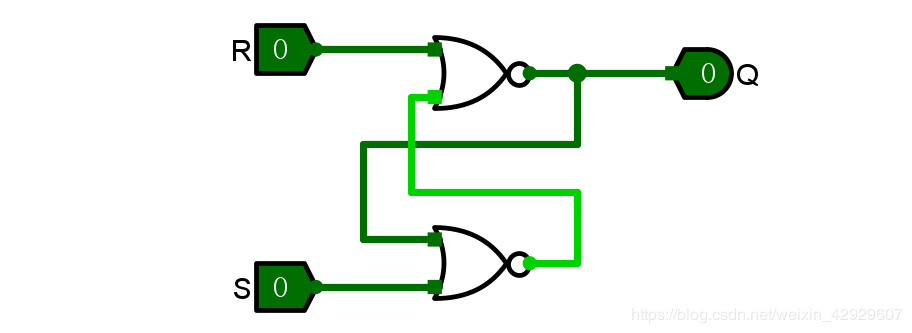

2 R-S 锁存器

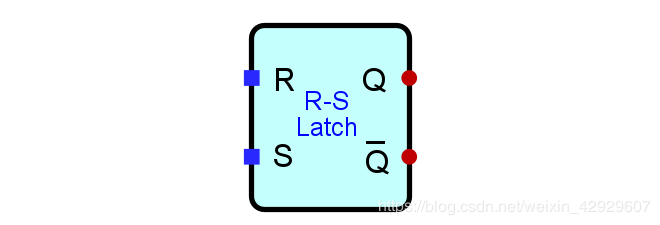

2.1 基本结构

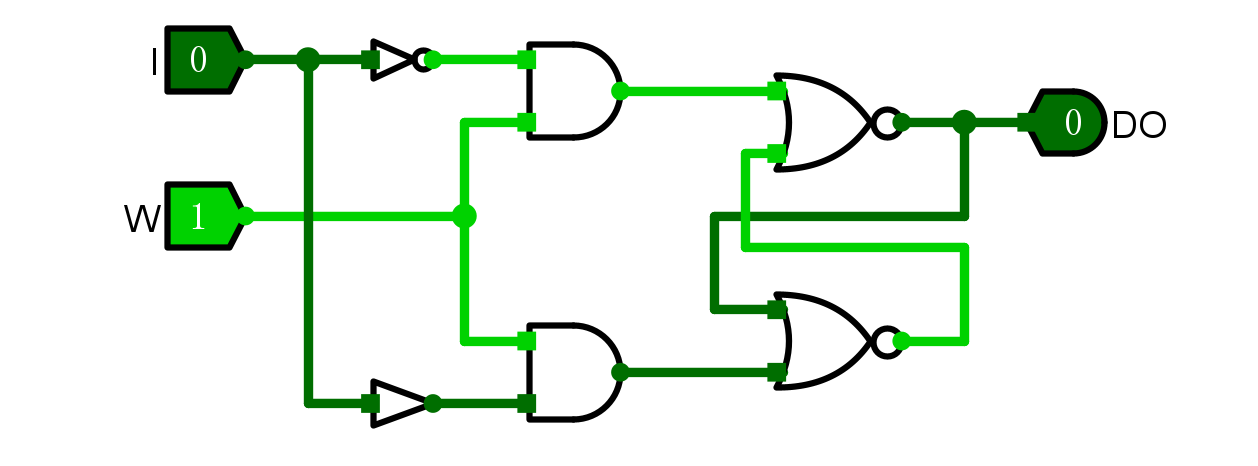

我们来看一下他=它的结构,通常有两种描述方法:

描述 1

描述 2

这两种结构完全一样,只不过放置的方式不一样,通常我们会采用描述 2 的方式。

可以看到,R-S 锁存器包含了 2 个或非门,2 个输入端口,1 个输出端口,这个结构真的简单至极。

如果你学过一点数字逻辑的知识,也许你会跟我争辩,R-S 锁存器不是 2 个输出端口吗?先按照我说的继续往下听,之后会解释的。

2.2 如何锁住 1-bit

那么,这样一个结构,如何锁住(存储)1-bit 的?

为了方便描述,我们先为上面的结构命名一下。

2 个输入端口分别命名为

R和S1 个输出端口被命名为

Q

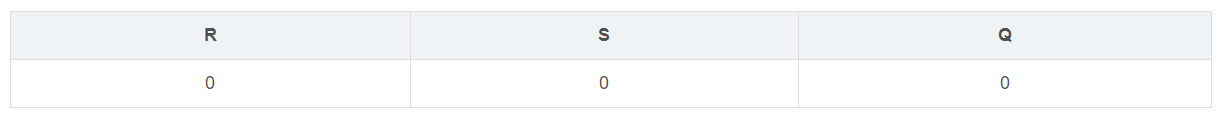

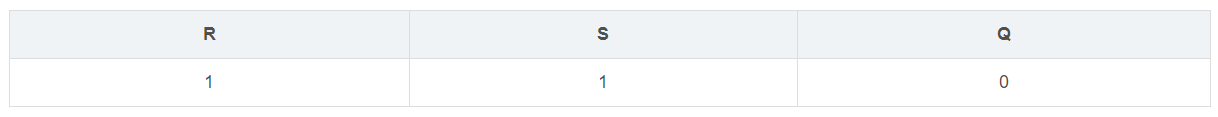

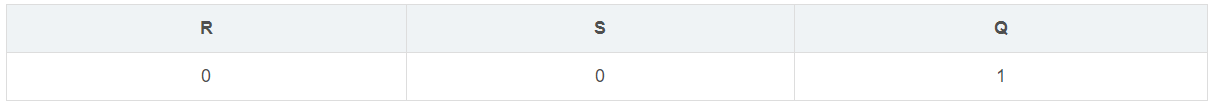

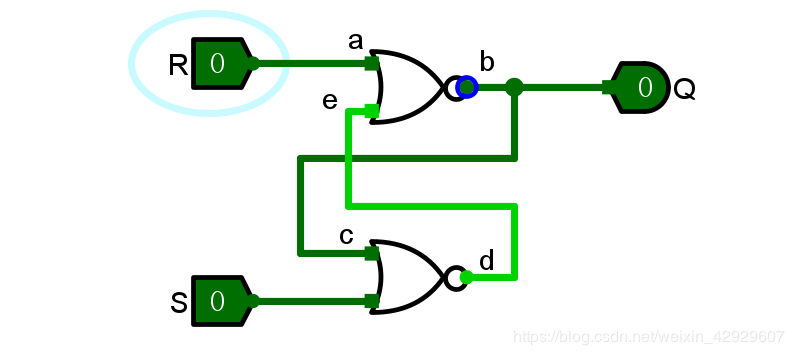

让我们记住这个初始状态

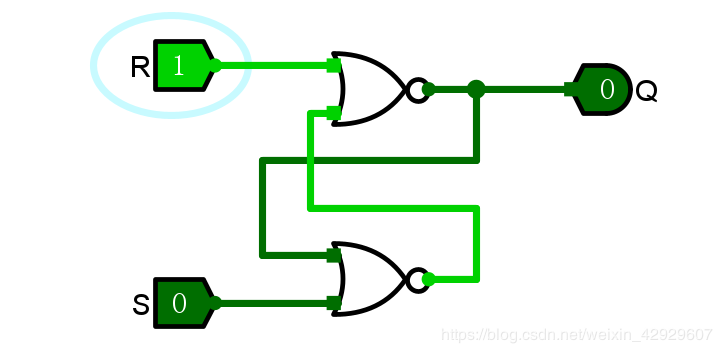

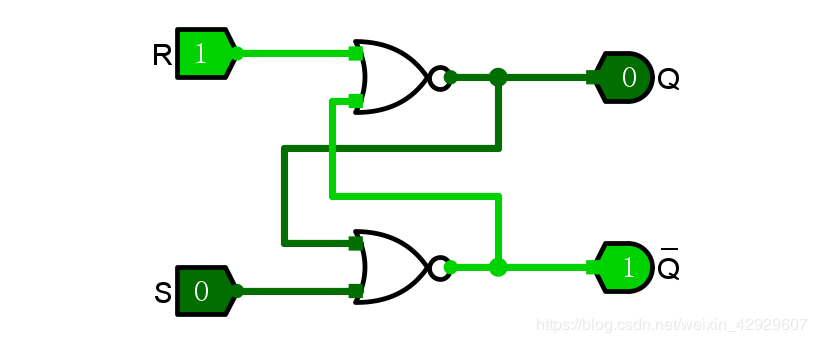

然后,我们将R置为 1。

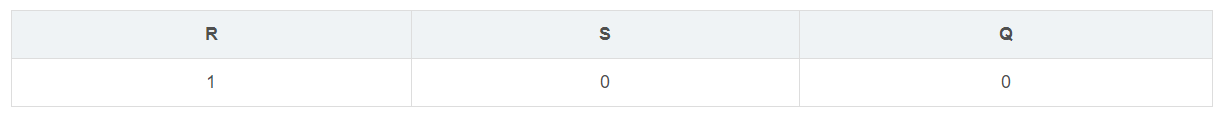

你会发现,此时的状态是

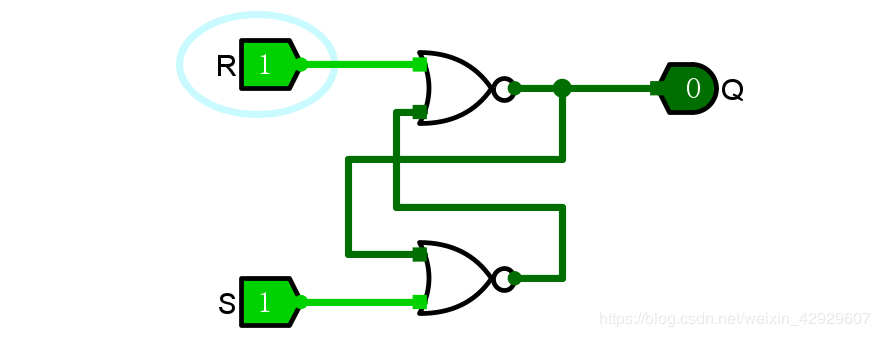

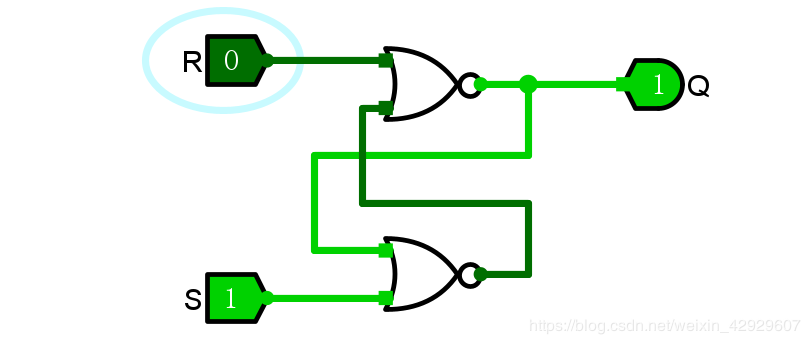

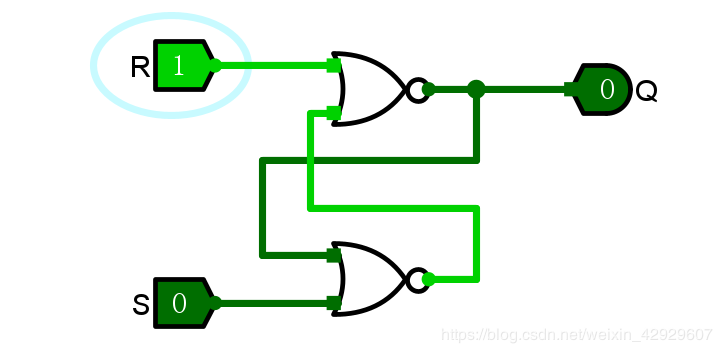

我们再将S置为 1

此时的状态是

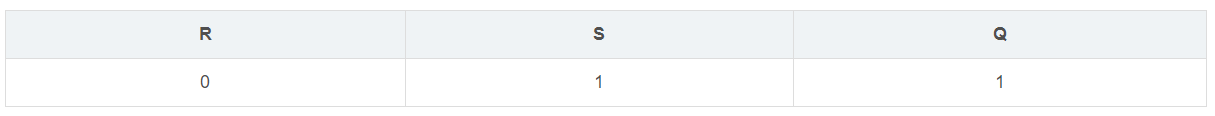

我们再将R置为 0

此时的状态是

我们再将S置为 0

此时的状态是

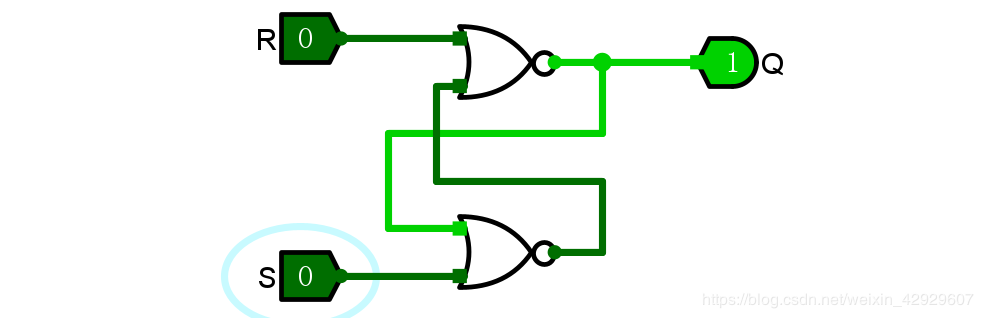

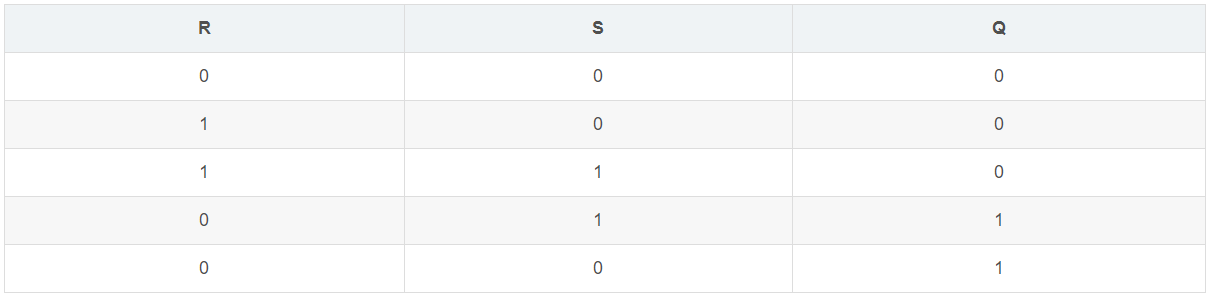

接下来,我们汇总一下上面的几种状态

我们可以看到,同样是0,0,但是输出却可能是0或1,这也就意味着,这不是组合逻辑,而是时序逻辑,输入的顺序会影响结果。

同时,我们再继续进行实验可以发现(此处请自行完成实验,亲自体验以下结论)

一旦置

R = 1,S = 0,S 不变的情况下,无论 R 如何改变,Q 都等于 0一旦置

R = 0,S = 1,R 不变的情况下,无论 S 如何改变,Q 都等于 1当

R = 0,S = 0的时候,Q 的结果,取决于上一个状态。如果之前是因为R = 1,S = 0导致的Q = 0,则现在的 Q 依然 0;如果之前是因为R = 0,S = 1导致的Q = 1,则现在的 Q 依然为 1一旦置

R = 1,S = 1,Q 一定等于 0,这种情况与我们的目标不符,我们需要禁止它

因此,我们得到了 R-S 锁存器特性表

我带你分析完了这些,我们改回看主题,看一下它是如何锁住 1-bit 的。我们看一下刚才描述的状态:

一旦置

R = 1,S = 0,S 不变的情况下,无论 R 如何改变,Q 都等于 0一旦置

R = 0,S = 1,R 不变的情况下,无论 S 如何改变,Q 都等于 1

我们观察后面加粗的句子,不难看出,1 个二进制数被“锁在”了器件中,这也就是所谓的锁存器,它在功能上,实现了存储 1 个二进制位。

2.3 为什么可以锁住 1-bit

刚才,我们知道了 R-S 锁存器能够存储 1 个二进制位,并且已经达成了目标,是的,我们成功存储了 1 个二进制位,但是,这还不够,我们应该保持好奇心,问一问自己,为什么能够锁住?

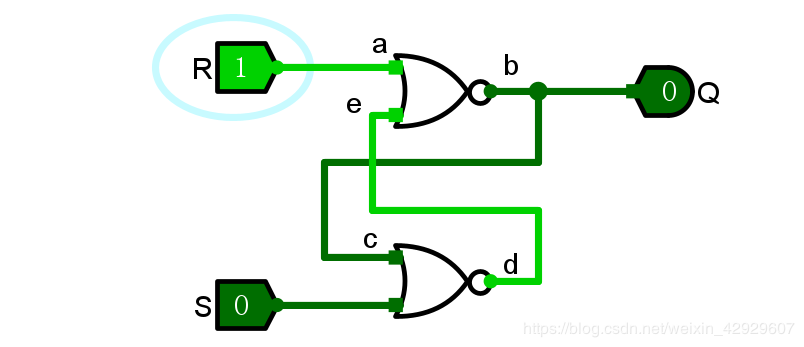

让我们来分析一下 R-S 锁存器的工作,以R = 1,S = 0为初态举例。

下面是初态,并且我在几个关键的地方做了标记。

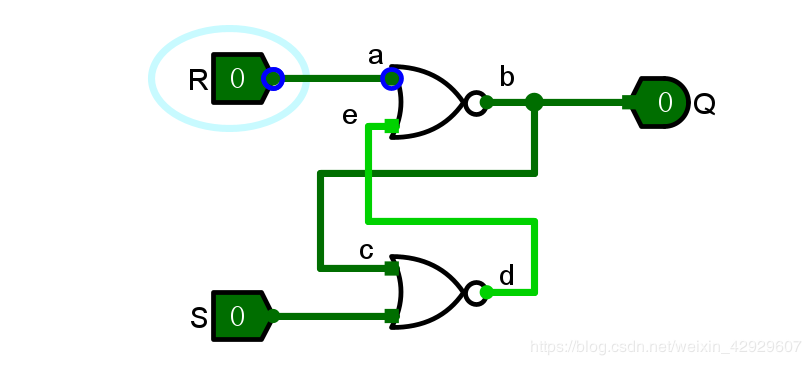

之后,我令R = 0,我们来逐步地分析一下,到底发生了什么。

首先,0信号传到了a端,此时a = 0

然后,a和e进行或非运算,得到的结果传到了b端,此时b = 0

然后 b 端的结果,反馈到了 c 端,c = 0;之后,可以得到d = 1;之后,d 端的结果又**反馈**到了 e 端,可以得知,e = 1并没有发生变化,就此,这个过程就稳定了下来,b 端输出到 Q 的数据也就是最终结果了。

我们梳理一下这个过程,在令R = 0之后,只有 a 端的数据变为了 0,其他端口的数据均没有变化,这样一来,也就产生了锁住数据的现象,产生这种现象的原因,是因为反馈回路的存在。

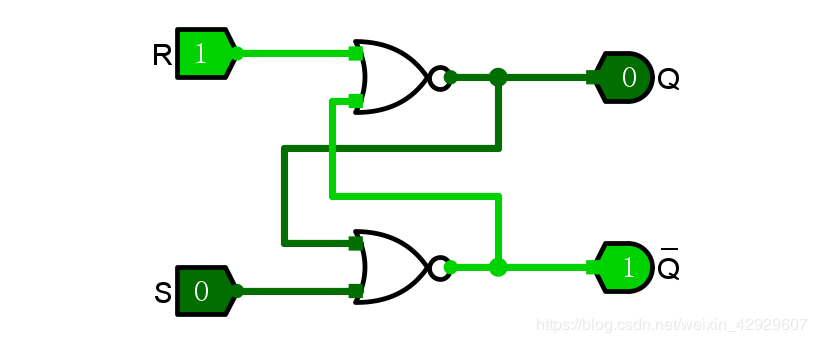

我们可以知道,bc锁住了0,de锁住了1,这二者正好相反,因此我们有时候也会将 R-S 锁存器设计为下面的样子,这样可以获得两个一直相反的输出结果

其中,上面读作输出 Q,下面读作输出 Q 拔,二者的取值永远相反,你也能够理解,为什么之前我们禁止了R = S = 1的情况,因为这样输出就不相反了,与设计目标不符。

2.4 为什么叫“R-S 锁存器”

为什么这个器件被命名为 R-S 锁存器呢?为什么不叫别的名字?

我们要知道,凡是命名,都有其含义,都能表达其意义,这样的命名才有价值,R-S 锁存器也是如此。

它是英文名称是:Set-Reset latch,有被称为 S-R Latch 或者 R-S Latch

我们来解释一下

R 就是

reset,重置、复位的意思,所以,当仅有它为 1 的时候,输出Q = 0S 就是

set,设置、置位的意思,所以,当仅有它为 1 的时候,输出Q = 1Latch,锁存器的意思,它能够存储 1 个二进制位

2.5 R-S 锁存器的功能

R-S 锁存器,也可以被称为置位复位触发器,我想你明白这个含义了,现在我们只是总结一下。

3 锁存器的核心和本质

通过 R-S 锁存器,我们可以理解锁存器的本质,掌握一类锁存器的核心,这才是我们要关注的重点内容,至于锁存器的设计和样子,不是最重要的,那只不过是在核心的基础之上,套上了外壳,从而让其拥有更广泛的的应用。

关于核心套外壳,我有必要进一步解释一下,我们知道,计算机领域又很多核心部件,例如 CPU,这是被外国垄断的高科技器件,它是核心,而计算机其他的部分,内存、硬盘、显示器等等,都是外壳,我们给核心套上不同的外壳,就构成了不同的计算机,能够进行不同的应用;又比如富士康代工厂,他们做的就是给核心套上外壳的工作。

我想你应该能够理解核心的重要性了。

那么锁存器的核心是什么?

这就是锁存器的核心,原理方面,我之前已经详细讲解过,不再赘述,但是希望你认真对待那些看似简单容易的知识,因为它们可能蕴含着拥有无穷力量的核心思想。

3.1 核心套外壳的产品

那么核心套外壳之后,有那些产品呢?有很多,例如:

基本 R-S 锁存器

门控 R-S 锁存器

D 型锁存器

甚至,由此核心,还可以构成各种各样触发器。

需要注意的是,这些外壳,并不是死板的,你完全可以根据需要,灵活地变化他们,不必拘泥于某种特定的形式,不过前提是,变化之后的产品真的很好用,否则,你更应该直接使用封装好的产品。

后面的小节,我会为你详细讲解核心套外壳的产品。

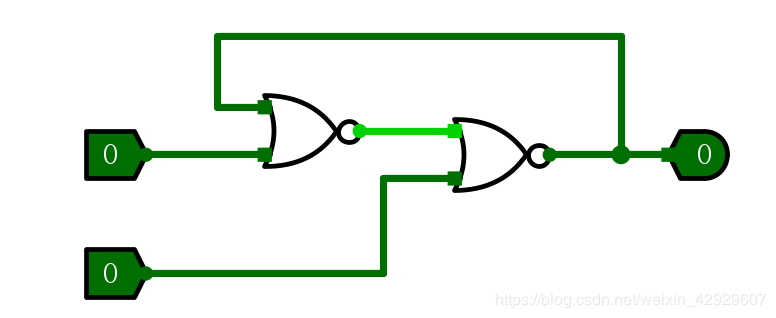

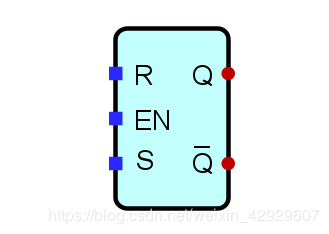

3 外壳一:基本 R-S 锁存器

嘿!一个新的目标出现了,之前我们为了存储 1 位数据,制作了 R-S 锁存器,现在,我们需要存储一位数据,并能够让他输出存储的数据,以及和存储数据互补(0 和 1 在二进制下是互补的)的数据。

这个产品我不再分析,因为你之前见过了:

现在我们将其封装一下,让它更像一个产品。

至于它的功能,我想你已经知道了,基本 R-S 锁存器,增加的外壳是一个输出端口。

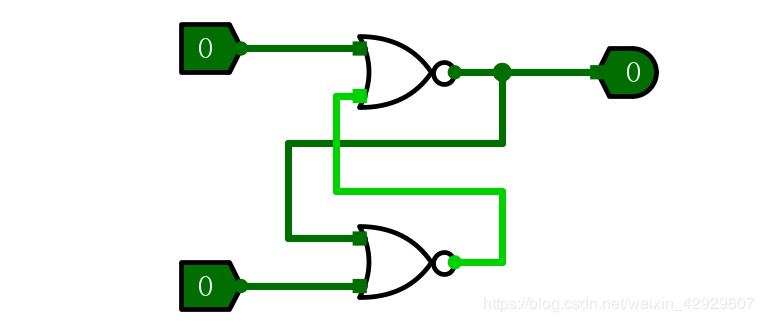

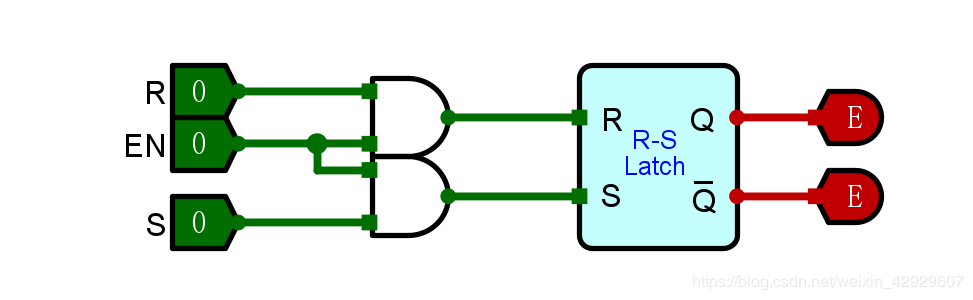

4 外壳二:门控 R-S 锁存器

现在,新的任务又下达了,我们的基本 R-S 锁存器,可以随意被使用,这可不好,现在我们需要增加一个开关,只有开关打开的时候,基本 R-S 锁存器才可以被使用。

我们考虑一下,看看上面封装好的基本 R-S 锁存器,我们可以加的外壳是:在进入 R、S 输入端口之前,增加 2 个与门,这样就可以控制输入信号的有效、无效。

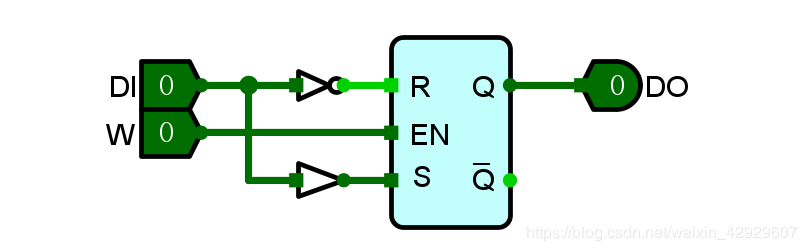

你可以试一试这个电路,这就是门控 R-S 锁存器。

名称的含义,门控,就是加一个开关,它被称为使能端(Enable terminal),简写EN。

我们将它封装一下:

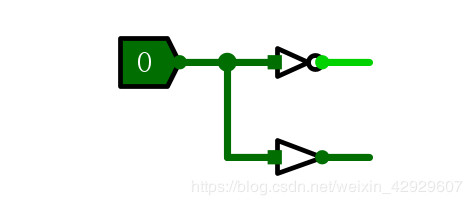

5 外壳三:D 型锁存器

全新的任务

彻底禁止掉

R = S = 1的情况,对于任何输入的数据,使其,不可能存在这种情况,保证安全,完全避免非法状态。让这个器件能够实现数据 0 和 1 的写入,并且能够控制是否写入。

我们由门控 R-S 锁存器开始思考,既然 R 和 S 不能相同,那就只能相反了,这样虽然会舍弃掉R = S = 0的情况,不过,既然这种情况会与上一个状态相同,而上一个状态 R 和 S 一定相反,所以,舍弃掉又有何妨呢?因此,我们的思路就有了,让 R 和 S 永远相反,我们怎么做呢?我想你应该知道了,使用 1 个输入端和 1 个非门!

就像下面这样,加缓冲器是为了让数据流动时间和加了非门的线路同步

那么第二个目标如何达成?显然我们已经完成了一部分,1 个输入端和 1 个开关我们已经有了,我们只需要,去掉 Qbar 即可。

你会发现,这里有了较大的变化,我的节奏加快了,如果你前面认真实践了的话,我想你是适应这种变化的。

我来解释一下这些变化

为了达成目标,我们要让 R 和 S 的值一直相反,因此我们加了一个非门和缓冲门,用一个输入端操控它,注意,不要将非门放错位置,你仔细想一下会明白怎么放置的(举一个例子就好,例如

DI = 0的时候,如何让DO = 0)。我们将开关作为写入端

我们不使用 Qbar 端口

我来解释一下端口名称的变化

DI:数据输入端,可以控制输入的数据是 0 还是 1

DO:数据输出端,可以读取存储在锁存器中的数据

W:写入端,可以控制是否将数据写入端的数据写入到锁存器中

1. 若W = 1,则 DI 中的数据会被写入到锁存器中,并且存储起来,此时,DO 读取的数据是和 DI 一样的

2. 若W = 0,则 DI 中的数据不会被写入到锁存器中,此时,DO 将会读取锁存器中存储的数据,与 DI 的数据无关

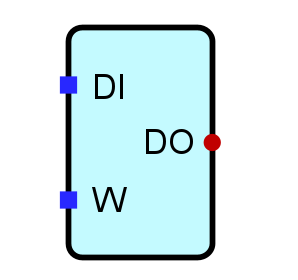

我们封装一下这个器件

6 思考题 &预告

我留下思考题和预告,请你仔细思考并认真实践

最初,我们使用或非门构造了 R-S 锁存器,事实上,与非门一样可以完成这件事情,我在 3.1 节提过,产品的设计的不能死板,它是灵活的,请你思考一下如何设计。

请思考一下,具体讲解的几种外壳,有没有感受到,外壳的设计也又核心思想支撑? 之后我们会揭秘。

核心套外壳的产品,也完全可以作为新的核心,为他们再赋予外壳,做出更多有用的产品。

我们的目标是构建一个 RAM 存储器,以 R-S 为锁存器的 RAM 产品,随着时代的发展,它的性能提升进入了瓶颈期,这个时候,人们的最佳选择是优化核心,这也由 RAM 存储器,转变成了 SRAM、DRAM 等类型的存储器,这些后面也会提及(也可以按照此思路,去想一想:算盘-->计算器-->电子计算机-->量子计算机)。

备注:此文章我在也 CSDN 发表了,因此图片有水印。

版权声明: 本文为 InfoQ 作者【姜海天】的原创文章。

原文链接:【http://xie.infoq.cn/article/3299da0377e9b33c73e11ab88】。

本文遵守【CC BY-NC-SA】协议,转载请保留原文出处及本版权声明。

评论